Since 1965, Moore’s law – engineer Gordon Moore’s astute observation that the number of transistors on chips will double each year to keep up with the needs of technology – has remained true.

At one point, Moore’s law was adjusted to the number of transistors doubling every 18 months as they got smaller and smaller and harder to pack into chips.

But as Moore’s law continues to be stretched to its limits annually in recent years by the demands of chips and technology, there might be a better measure of technological progress, says Aart De Geus, the chairman and co-CEO of electronic design automation (EDA) and semiconductor IP design firm, Synopsys.

The better standard is what de Geus calls “SysMoore,” which he says is the blending of long-held Moore’s law insights with new technology innovations that leverage systemic complexity.

“Every vertical market right now is investing to use AI to become a little smarter, more efficient, more effective,” de Geus said in his opening keynote, “Builders of the Imaginary: From Artificial Intelligence to Artificial Architects in the Era of SysMoore,” at the virtual AI Hardware Summit on Sept. 14. “But with it comes a whole set of system requests and requirements that all have to be integrated. Well, this is what characterizes the SysMoore Era.”

So how are they different?

SysMoore, fundamentally, stands for systemic complexity, in contrast to scale complexity, which has for years been supported by the exponential ambition that we know from traditional Moore's law, said de Geus.

Still, however, Moore’s law remains relevant, he said. “I am the first one to say that Moore's law is by no means dead,” de Geus said. “We are continuing to smaller devices.”

At least one chipmaker recently said it will no longer use dimensions in nanometers to describe the size of its chips, foregoing a 2nm moniker and instead preparing to measure its chips in angstroms, said de Geus. Instead of 2nm, that company’s chips will be described as 20 angstroms in size, he added.

“I do notice that in the word angstrom, is the word angst, and we will have to deal with a lot of technical challenges to overcome that [size constraint].”

To make these leaps to ever more powerful and smaller chips, changes are needed that are much more complex than the Moore’s law chip developments of the past, he said.

“And there is a lot to do,” said de Geus. “One of the considerations is we need to increase productivity. And as a matter of fact, we would predict that in this decade, we need to increase it by about 1,000X to live up to the ambitions that together we have.”

Those goals will not be possible if we stick with the Moore’s law constraints of the past, de Geus said, addressing chip designers who will be tasked with imagining, designing and building the next generations of chips and systems.

“Actually, you are sitting at the beginning at the dawn of a new era, SysMoore, systemic complexity, but with a Moore's law ambition,” he said. “And you are sitting in the middle of that because you determine the options of the architecture, and you determine how they will support the opportunities above and let us implement optimality below.”

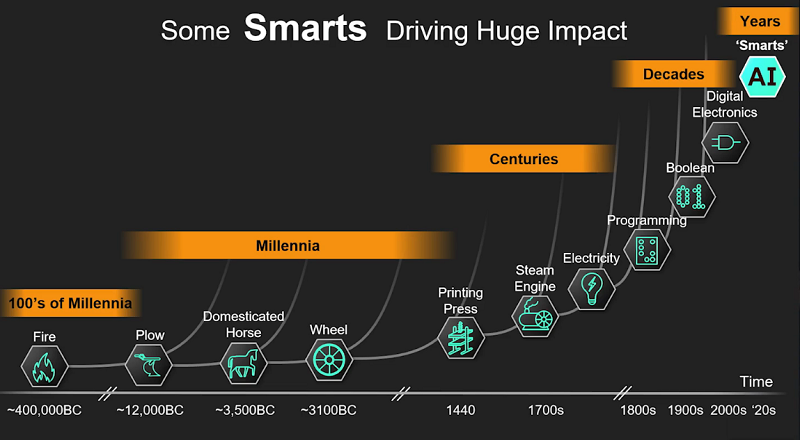

All of this lays out the mission for chip designers using technologies such as AI and machine learning to create more powerful and smaller chips over the next 20 years, said de Geus. “Your mission will be to architect intelligence [and that] is a highfalutin word. Let's humble it down just a little bit. Let us call it architecting smart” – a process that has been going on for some time and has resulted in many advancements and impacts on our lives, he said.

All of this lays out the mission for chip designers using technologies such as AI and machine learning to create more powerful and smaller chips over the next 20 years, said de Geus. “Your mission will be to architect intelligence [and that] is a highfalutin word. Let's humble it down just a little bit. Let us call it architecting smart” – a process that has been going on for some time and has resulted in many advancements and impacts on our lives, he said.

To make all of this happen, Synopsys is using more and more AI in chip design, which brings in AI to help map put and plan chips and how they are laid out and built at the silicon level, he said.

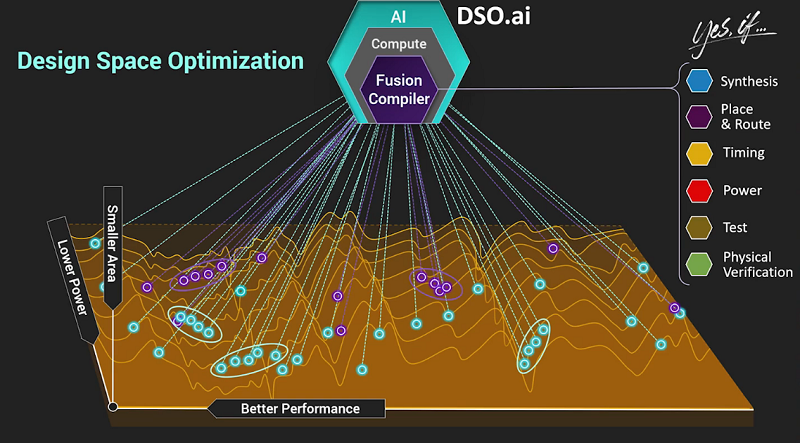

“We wrap some computation around it, we now let AI decide what to do,” he said. “And we aim not at design space exploration, but design space optimization, ergo the platform name of DSO.ai (Design Space Optimization). So, we have a whole new design platform that uses literally everything we have learned in the past.”

Using these tools, the company is experimenting with chip voltages, chip architectures down to the laying out of circuits and wires on the chips, and a myriad of factors in between to find ways that AI can improve designs and chip performances under the mantra of SysMoore.

“The bottom line of all of this is we have made enormous progress, but it begs the question where we're going to go next,” said de Geus. “Walter Gropius and other well-known [building] architects said that architecture really begins where engineering ends. Well, we have no intent whatsoever to end engineering. Our job is to raise the level of optimality because it raises the entire picture.”

In the future, that could mean adding some micro-architectural optimizations to raise the bar for the architects that can use these processes, he said.

And then in the longer term, maybe at some point in time, it is even possible to revisit some aspects of functionality, maybe go as far as touch the software that is running on the chip that one wants to optimize for,” said de Geus.

In July, the company made some progress in this direction, he said, by experimenting with optimizations for timing and power using DSO.ai and seeing power improvements of five percent to start.

By adjusting the clocks, more optimizations were made, providing another 13 percent power improvements, which were substantial, he said. “The ultimate ambition is to see if we can do something even in the functional space. And what that really means is a very big step into a different dimension, because that really means now going for total power.”

By adjusting the clocks, more optimizations were made, providing another 13 percent power improvements, which were substantial, he said. “The ultimate ambition is to see if we can do something even in the functional space. And what that really means is a very big step into a different dimension, because that really means now going for total power.”

Using AI, the improvements were possible, which shows that everything in the food chain matters, he said. “You change a transistor, it matters, you change the software, it matters and everything in between.”

And when combined, the improvements are particularly notable, he said.

“If you multiply these numbers out, what you get here is a 25.6 percent improvement,” said de Geus. “That is in the league of a whole technology node or two. That is how big this is. We know what to do next, which is we are going to continue to push optimization into this picture moving to more and more aspects, higher and higher levels of abstraction, knowing perfectly well that the difficulty level will increase because they all intersect.”

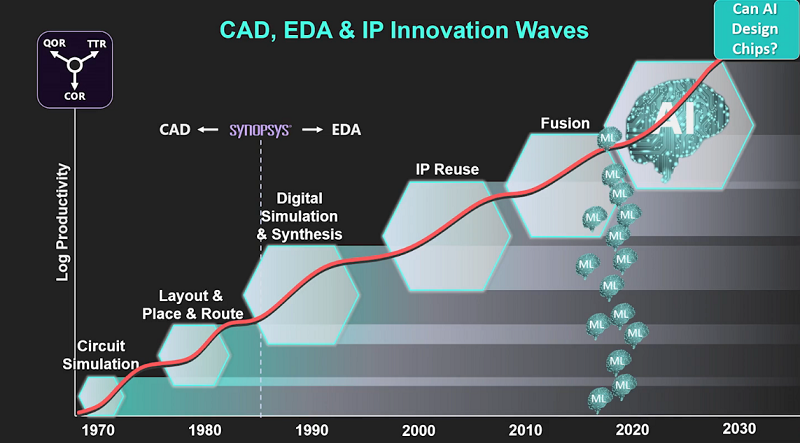

“Now to do great chips, which you have done, it takes multiple ingredients,” said de Geus. “You need advancements in technology nodes, scaling of manufacturing, and the ability, of course, to test if something works. But you also need the ability to design using EDA (Electronic Design Automation), IP re-use, and by the way, you have to build in the testing.”

At Synopsys, which has been working on EDA and semiconductor design for 35 years, the company sees the future of a SysMoore roadmap, he said.

Technology since the days of humans in caves initially emerged slowly, with the development of fire, hunting, growing food and the arrival of the earliest alphabets and printing presses taking a long time. Later as the industrial revolution arrived, new technologies came more quickly, from electricity to commercial farming to manufacturing, automobiles, airplanes and much more. That changed as new inventions and developments arrived at a much faster pace.

“Then the wonders of lithography and planar transistor technology, all supported by design, EDA and IP has made the modern age and most importantly, Moore's law possible,” said de Geus. “This is the most rapidly increasing [development] exponential in history. Now if you put this in the big picture, what we really see is that we are surrounded by two massive forces, still better silicon and software that impacts everything.”

“Then the wonders of lithography and planar transistor technology, all supported by design, EDA and IP has made the modern age and most importantly, Moore's law possible,” said de Geus. “This is the most rapidly increasing [development] exponential in history. Now if you put this in the big picture, what we really see is that we are surrounded by two massive forces, still better silicon and software that impacts everything.”

The new SysMoore era is characterized by the notion of function and form, and Synopsys will be a part of that progress, de Geus added.

“Form must fit the function,” he said. “I would argue that great engineers are often also great artists because we can imagine the impossible, and we can deliver when the rubber meets the road.”

Related

"chips" - Google News

September 21, 2021 at 02:56AM

https://ift.tt/3nS4k7g

From Moore's Law to SysMoore: AI, Chip Design and How Gordon Moore's Idea Might Be Changing - EnterpriseAI

"chips" - Google News

https://ift.tt/2RGyUAH

https://ift.tt/3feFffJ

Bagikan Berita Ini

0 Response to "From Moore's Law to SysMoore: AI, Chip Design and How Gordon Moore's Idea Might Be Changing - EnterpriseAI"

Post a Comment